Product Summary

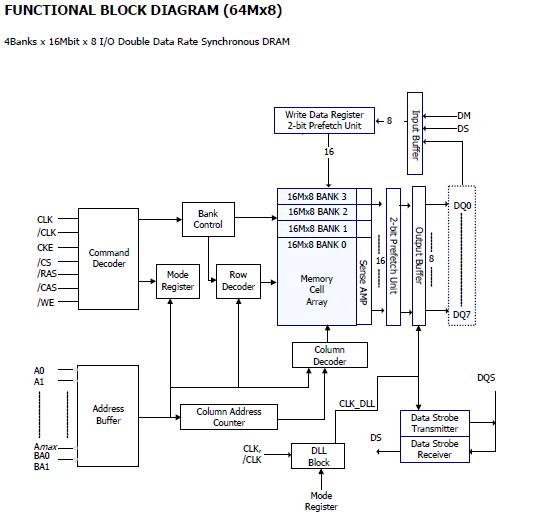

The HY5DU121622DTP-J is a 536,870,912-bit CMOS Double Data Rate(DDR) Synchronous DRAM. It is ideally suited for the main memory applications which requires large memory density and high bandwidth. The HY5DU121622DTP-J offers fully synchronous operations referenced to both rising and falling edges of the clock. While all addresses and control inputs are latched on the rising edges of the CK (falling edges of the /CK), Data, Data strobes and Write data masks inputs are sampled on both rising and falling edges of it. The data paths of HY5DU121622DTP-J are internally pipelined and 2-bit prefetched to achieve very high bandwidth. All input and output voltage levels are compatible with SSTL_2.

Parametrics

HY5DU121622DTP-J absolute maximum ratings: 1)Operating Temperature (Ambient), TA: 0 ~ 70℃; (2)Storage Temperature, TSTG: -55 ~ 150℃; (3)Voltage on VDD relative to VSS, VDD: -1.0 ~ 3.6 V; (4)Voltage on VDDQ relative to VSS, VDDQ: -1.0 ~ 3.6 V; (5)Voltage on inputs relative to VSS, VINPUT: -1.0 ~ 3.6 V; (6)Voltage on I/O pins relative to VSS, VIO: -0.5 ~3.6 V; (7)Output Short Circuit Current, IOS :50 mA; (8)Soldering Temperature Time, TSOLDER: 260 . 10℃ Sec.

Features

HY5DU121622DTP-J features: (1)VDD, VDDQ = 2.3V min ~ 2.7V max (Typical 2.5V Operation +/- 0.2V for DDR266, 333); (2)VDD, VDDQ = 2.4V min ~ 2.7V max (Typical 2.6V Operation +0.1/- 0.2V for DDR400, 400Mbps/pin product and 500Mbps/pin product ); (3)All inputs and outputs are compatible with SSTL_2 interface; (4)Fully differential clock inputs (CK, /CK) operation; (5)Double data rate interface; (6)Source synchronous - data transaction aligned to bidirectional data strobe (DQS); (7)x16 device has two bytewide data strobes (UDQS, LDQS) per each x8 I/O; (8)Data outputs on DQS edges when read (edged DQ) Data inputs on DQS centers when write (centered DQ); (9)On chip DLL align DQ and DQS transition with CK transition; (10)DM mask write data-in at the both rising and falling edges of the data strobe; (11)All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock; (12)Programmable CAS latency 2/2.5 (DDR266, 333) and 3/4 (DDR400, 400Mbps/pin product and 500Mbps/pin product) supported; (13)Programmable burst length 2/4/8 with both sequential and interleave mode; (14)Internal four bank operations with single pulsed/RAS; (15)Auto refresh and self refresh supported; (16)tRAS lock out function supported; (17)8192 refresh cycles/64ms; (18)60 Ball FBGA Package Type; (19)Lead free (ROHS Compliant).

Diagrams

|

HY5DS113222FM |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5DS283222BF |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5DS283222BFP |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5DS573222F |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5DS573222P |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY5DU121622A |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))